The RV870 Story: AMD Showing up to the Fight

by Anand Lal Shimpi on February 14, 2010 12:00 AM EST- Posted in

- GPUs

Process vs. Architecture: The Difference Between ATI and NVIDIA

Ever since NV30 (GeForce FX), NVIDIA hasn’t been first to transition to any new manufacturing process. Instead of dedicating engineers to process technology, NVIDIA chooses to put more of its resources into architecture design. The flipside is true at ATI. ATI is much less afraid of new process nodes and thus devotes more engineering resources to manufacturing. Neither approach is the right one, they both have their tradeoffs.

NVIDIA’s approach means that on a mature process, it can execute frustratingly well. It also means that between major process boundaries (e.g. 55nm to 40nm), NVIDIA won’t be as competitive so it needs to spend more time to make its architecture more competitive. And you can do a lot with just architecture alone. Most of the effort put into RV770 was architecture and look at what it gave ATI compared to the RV670.

NVIDIA has historically believed it should let ATI take all of the risk jumping to a new process. Once the process is mature, NVIDIA would switch over. That’s great for NVIDIA, but it does mean that when it comes to jumping to a brand new process - ATI has more experience. Because ATI puts itself in this situation of having to jump to an unproven process earlier than its competitor, ATI has to dedicate more engineers to process technology in order to mitigate the risk.

In talking to me Carrell was quick to point out that moving between manufacturing processes is not a transition. A transition implies a smooth gradient from one technology to another. But moving between any major transistor nodes (e.g. 55nm to 45nm, not 90nm to 80nm) it’s less of a transition and more of a jump. You try to prepare for the jump, you try your best to land exactly where you want to, but once your feet leave the ground there’s very little to control where you end up.

Any process node jump involves a great deal of risk. The trick as a semiconductor manufacturer is how you minimize that risk.

At some point, both manufacturers have to build chips on a new process node otherwise they run the risk of becoming obsolete. If you’re more than one process generation behind, it’s game over for you. The question is, what type of chip do you build on a brand new process?

There are two schools of thought here: big jump or little jump. The size refers to the size of the chip you’re using in the jump.

Proponents of the little jump believe the following. In a new process, the defect density (number of defects per unit area on the wafer) isn’t very good. You’ll have a high number defects spread out all over the wafer. In order to minimize the impact of high defect density, you should use a little die.

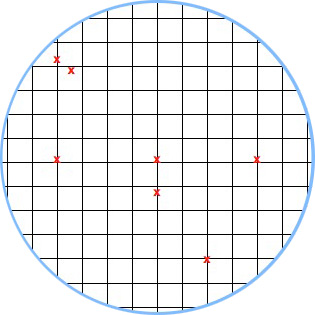

If we have a wafer that has 100 defects across the surface of the wafer and can fit 1000 die on the wafer, the chance that any one die will be hit with a defect is only 10%.

A hypothetical wafer with 7 defects and a small die. Individual die are less likely to be impacted by defects.

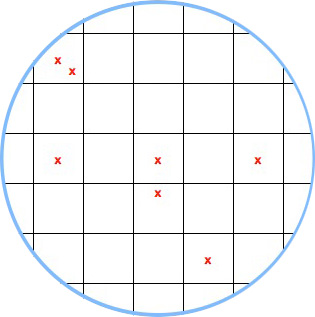

The big jump is naturally the opposite. You use a big die on the new process. Now instead of 1000 die sharing 100 defects, you might only have 200 die sharing 100 defects. If there’s an even distribution of defects (which isn’t how it works), the chance of a die being hit with a defect is now 50%.

A hypothetical wafer with 7 defects and a large die.

Based on yields alone, there’s no reason you’d ever want to do a big jump. But there is good to be had from the big jump approach.

The obvious reason to do a big jump is if the things you’re going to be able to do by making huge chips (e.g. outperform the competition) will net you more revenue than if you had more of a smaller chip.

The not so obvious, but even more important reason to do a big jump is actually the reason most don’t like the big jump philosophy. Larger die are more likely to expose process problems because they will fail more often. With more opportunity to fail, you get more opportunity to see shortcomings in the process early on.

This is risky to your product, but it gives you a lot of learning that you can then use for future products based on the same process.

132 Comments

View All Comments

Dudler - Sunday, February 14, 2010 - link

Whoa... Just Whoa.Very insightful and interesting.

Amd moving to GF next generation and Norther Islands this year?

Whoa.

Thx Anand :)

carlhenry - Sunday, February 14, 2010 - link

i really loved the eyefinity being so 'mission impossible'. awesome article!Patrick Wolf - Sunday, February 14, 2010 - link

The first rule of SunSpot: You don't talk about SunSpot. :Dmubeen - Tuesday, February 16, 2010 - link

Such an informative article Mr. Anand. Really appreciate your efforts.just4U - Tuesday, February 16, 2010 - link

I agree it's a great article, nice to see these ones pop up from time to time. It don't really matter to me if it's nvidia, amd or intel.. just having a more insightful read is refreshing.DearSX - Sunday, February 14, 2010 - link

I really do a like article like this. I wonder how old others are cause I'm 25 and I did not even notice how much reading things like this mattered. Its more important than buying something or performance figures imo.Paulman - Sunday, February 14, 2010 - link

I, too, will second that. Really cool. :PMrSpadge - Sunday, February 14, 2010 - link

Many thanks for this interesting article and especially the in-dpeth information about TSMC, the process and how ATI deals with it. Thanks to you, Anand, for writing it and thanks to the good guys at AMD for sharing this information!Beyond excellence :)

hyvonen - Monday, February 15, 2010 - link

And NVidia's call for "zero defects, zero variability" was jaw-dropping. Do they have any idea how silicon is manufactured?Unbelievable cluelessness... with this attitude, they are out of business in the next two years. They are completely unprepared to harness the potential in the latest process nodes.

Meanwhile, it also sounds like TSMC is way over its head in this - uncharacteristic screw-ups with the chamber matching, bad leakage etc. Not to mention the choice to delay HKMG until 28nm (and having to kill 32nm because of that). GF is going to eat them for lunch, and take over the foundry business.

ET - Sunday, February 14, 2010 - link

Indeed. One of the more interesting articles I've read in a while.